お断り

本稿は校正前です。デザイン確認のために一時的に公開しています。

誤字・脱字・タイポ・スペルミス等が多数あります。

各方面へのリンク(盗作はのぞく)や誤字脱字の御指摘は大変ありがたいのですが、このメッセージが消えてからにして頂けるようお願いします。

CPUのアーキテクチャ設計

コンピュータアーキテクチャとは

コンピュータアーキテクチャ(computer

architecture)には様々な意味がありますが、ここでは「プログラムカウンタとかアキュムレータというコンピュータを構成する機能素子をどのように並べて、どの様に接続するのか」を検討した結果という意味でこの言葉を使います。

CPUアーキテクチャ設計の実例

CPUの設計というと難しく聞こえるか知れませんが、どんなCPUでも必ず現れる部分構成が2つあります。この2つの部分構成がなぜ必ず現れるのかを理解できれば、CPUの設計はさほど難しいことではありません。(解らない方への補足資料は別途用意予定)

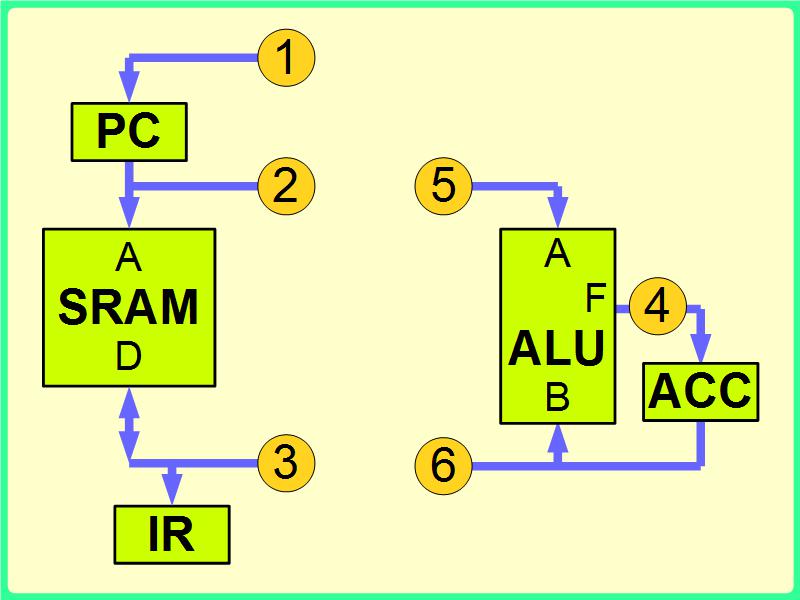

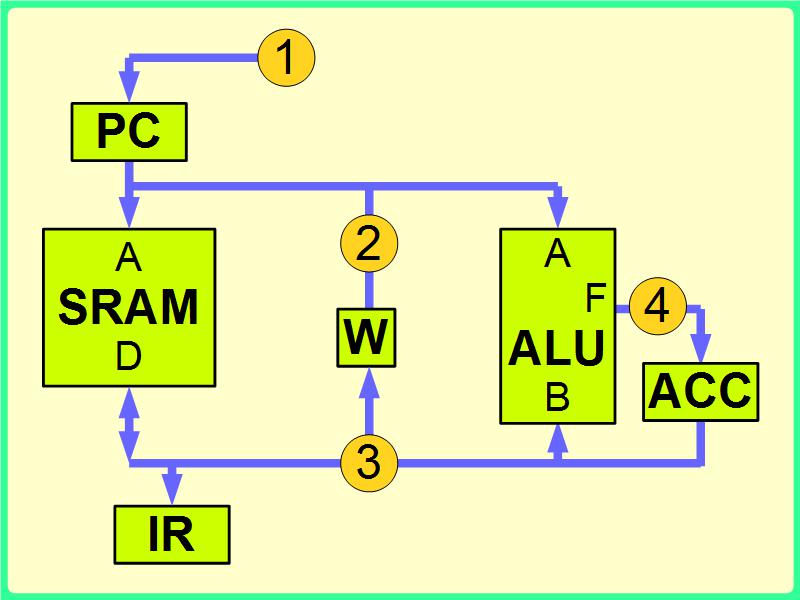

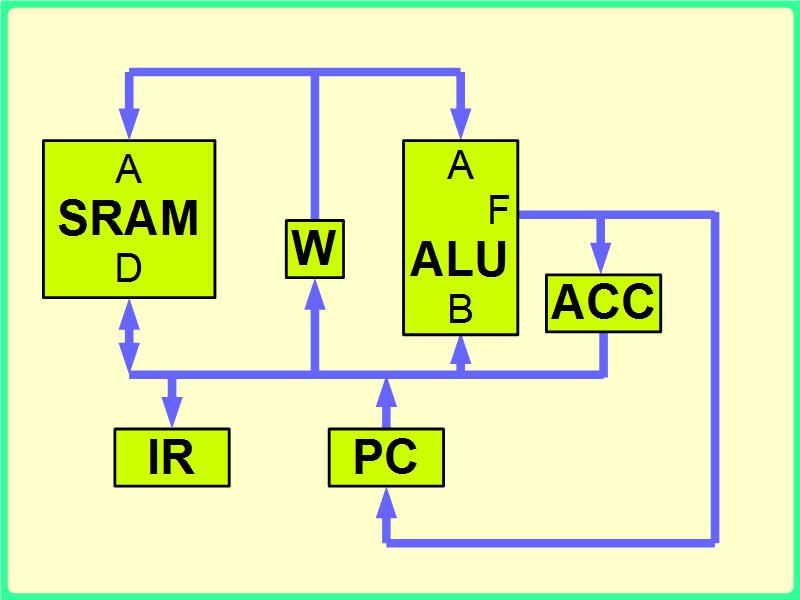

図1がその2つの部分構成です。 図の左半分はPC(プログラムカウンタ)がSRAM(主メモリ)のアドレスを指定し、そのアドレスの内容(=命令)をIR(インストラクションレジスタ)に格納するための接続です。

同じく右半分はACCの内容とALUのA入力に接続されるバスの値を演算して、その結果をACC自身に格納するための接続です。

実際には、左側の部分構成の①〜③と右側の部分構成の④〜⑥が何らかの形で接続され、全体としてコンピュータを形成することになります。

極論すれば、CPUのアーキテクチャ設計とは①〜⑥の「どこ」と「どこ」を接続するかを理論的に詰めていく作業だと言えます。

アドレスを指定するワークレジスタを追加

以後、図1を順次「進化」させて行く方法で、この図をコンピュータの構成図として完成させます。まずは主メモリに対するアドレスの指定手段の追加です。

プログラムカウンタが主メモリに対し、アドレスを指定するのは命令を取り出す時だけです。命令以外のデータを主メモリから読み書きする際は、プログラムカウンタ以外のレジスタがアドレスを指定しなければいけません。アキュムレータはメモリとのやり取りの相手ですから、アドレス指定には使えません。

結局どうしても一時的にアドレスを記憶するレジスタ(ワークレジスタ)が必要になります。

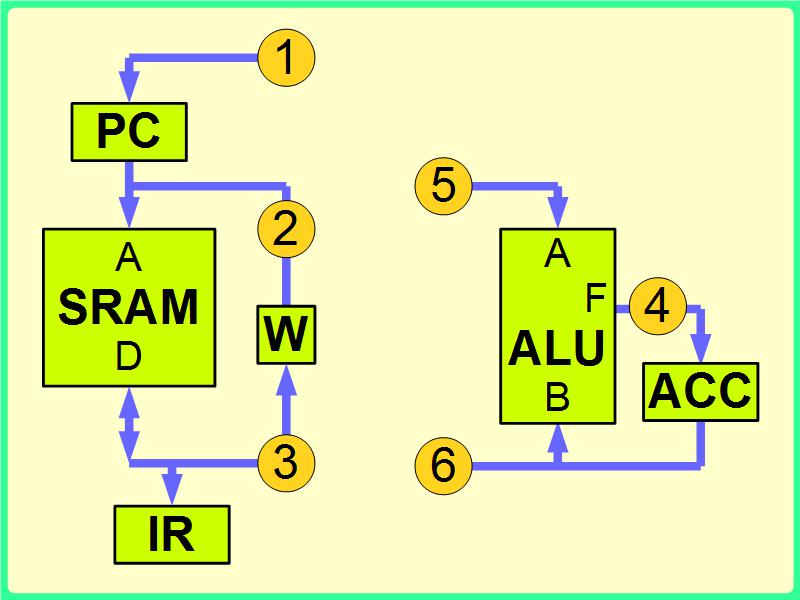

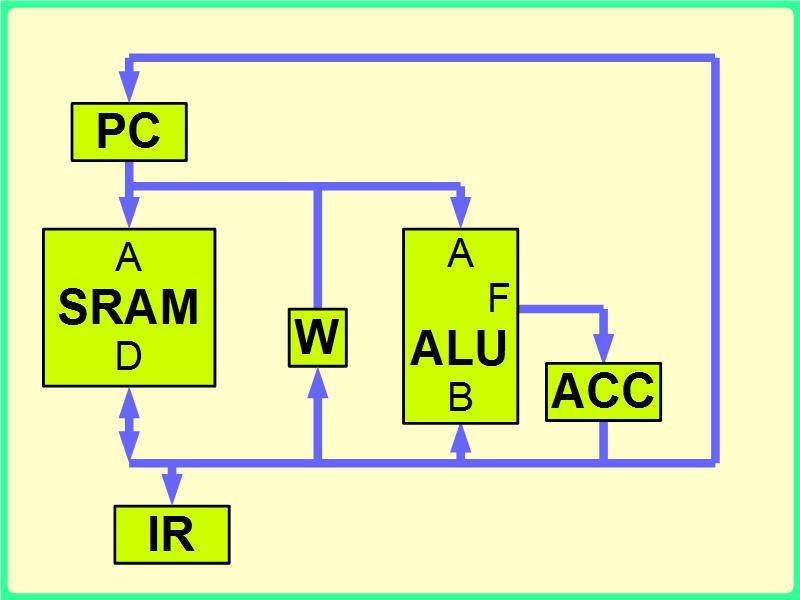

図2がワークレジスタを追加した図です。図中のWがワークレジスタで、その出力はSRAMのアドレス線②に、入力は同じくSRAMのデータ線③に接続します。

Wの値はIRに命令を格納するタイミングと同じタイミングで、主メモリの内容を書き込みます。

但し、IRには命令コードのオペコード部分をWには命令コードのオペランド部分のみを格納します。

(詳しい話は「命令設計編」で行います)

ストア命令の経路確保

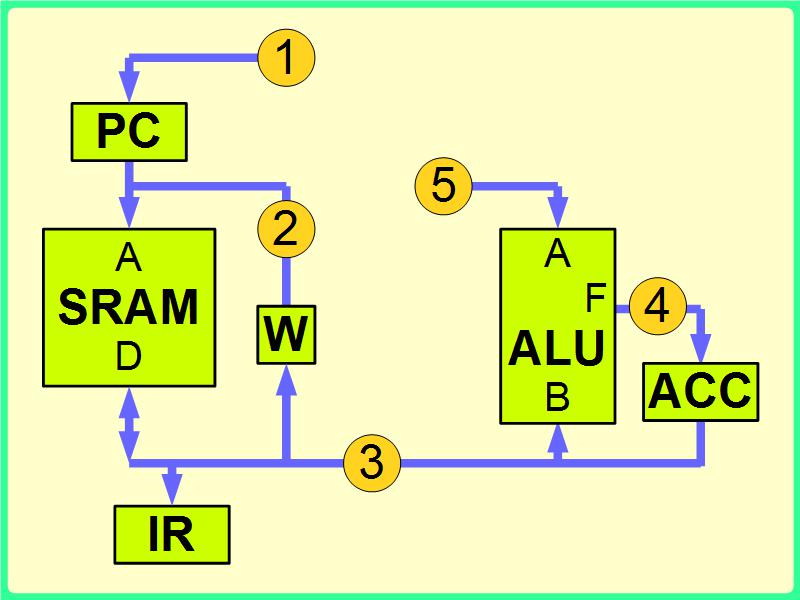

ストア命令はアキュムレータの値をメモリに書き込む命令ですから、アキュムレータの出力である⑥とメモリのデータ入力③(メモリはデータ入力線とデータ出力線が共通)を直結するだけです。

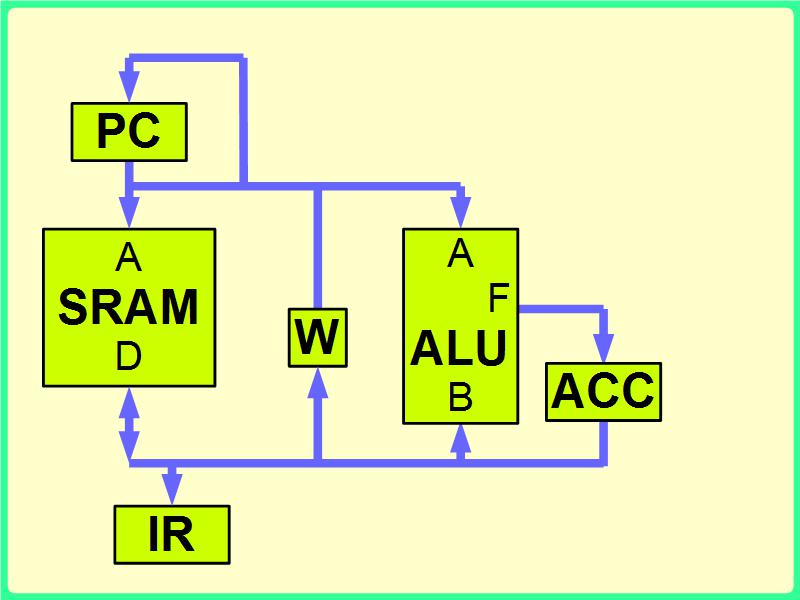

図3がストア命令に必要な接続を行った後の構成図です。

ACCの出力は経路③を通ってSRAMに格納されます。この時Wはストアするアドレスを保持する役割を持ちます。

演算命令の実現

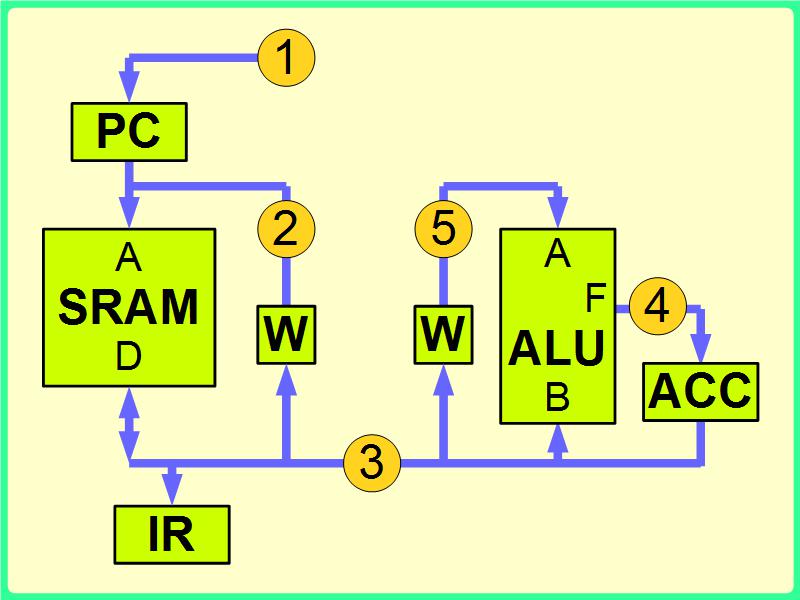

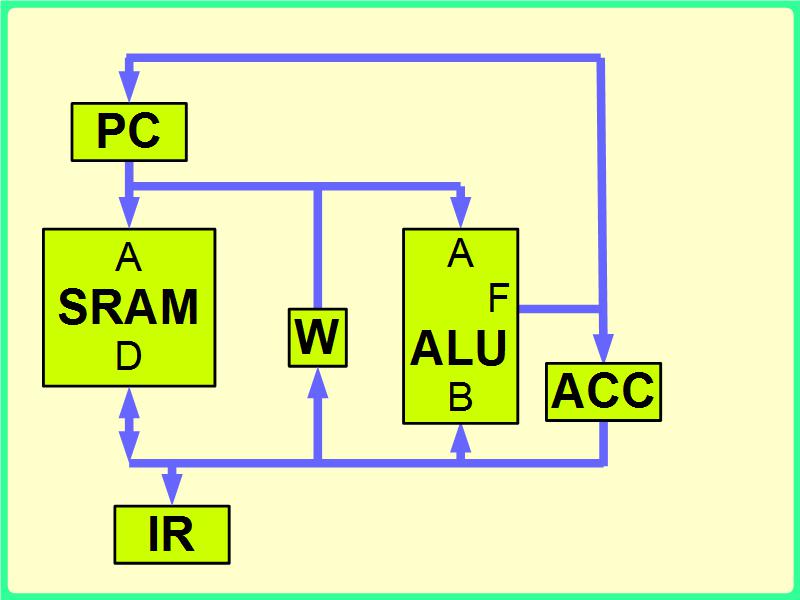

演算命令はアキュムレータの出力と主メモリの出力をALU(算術論理演算ユニット)に渡し、演算結果をアキュムレータ自身に格納する命令です。アキュムレータとALU間は既に経路が確立しているので、あとはアキュムレータ側ではないALUの入力⑤と主メモリのデータ出力③を接続するだけで良いのですが、一つ大きな問題があります。

SRAMのデータ線は既にアキュムレータに直結されているので、単に③と⑤を直結すると、ALUの2つの入力が短絡してしまいます。

これを防ぐには図4の様に、③と⑤の間にもワークレジスタが必要になります。

回路の簡略化

図4の構成はワークレジスタが2つ並んでいます。当然「2つのワークレジスタを1つにまとめれないか」という発想が浮かびます。とりあえず、2つのワークレジスタを1つにまとめた図を描いてみます。

図5が図4の2つのワークレジスタを一つにまとめた構成になります。

詳細はここでは省略(注)しますが、面白い事にこの構成でも、機能的には図4の構成と何ら遜色の無いコンピュータを構築できます。

当然のことながら、部品数が少なくて済むこちらの構成を軸として更に考察を進めます。

【注】詳しくは「命令設計編」で記述予定

分岐命令の分岐先指定経路確保

次の検討項目はプログラムカウンタの入力線(図5の①)をどこに接続するかです。

第一感としては、主メモリの出力に直接接続する(図6)、あるいはワークレジスタを介して主メモリの出力に接続する(図7)の2通りが思い付きます。

図6も図7も入出力回路がまだありませんが、その点を除くと十分に実用に値する最終構成です。特に図7の構成はプログラムカウンタに入出力が共通のものを使えるという利点もあります。

しかし、この構成ではいずれも相対ジャンプが実現できません。相対ジャンプ命令は必ずしも必要な命令ではありませんが、図6も図7もPCカウンタの出力が演算装置に接続されていますので、もう一工夫するだけで相対ジャンプ命令を実装できそうです。

図8は図5のPCの入力をALUの出力に接続して相対分岐命令を実現する構成案です。

これでも相対分岐命令(PCと、PCが示すSRAMの値とを加減算し、PCに格納する命令)はできます。

更なるアーキテクチャの改良

図8の相対分岐命令の実現方法の欠点は、PCが自分自身でアドレスを指定するSRAMの出力値を使って自分自身の値を変える命令であるため制御が若干煩雑になってしまうことです。

相対ジャンプの変位をあらかじめワークレジスタ(W)に格納し、ワークレジスタとプログラムレジスタの値を加減算してプログラムカウンタに格納することができれば制御回路はかなりすっきりします。

図9は図8のPCの位置を移動し、ワークレジスタとプログラムレジスタの値を加減算してプログラムカウンタ自身に格納できる様に改良したものです。

図9の短所はPCが直接とSRAMのアドレスを指定できないため、一度PCの値をWに格納してから、そのWの値でPCのアドレスを指定するという二度手間になる事です。

最強のアーキテクチャはどれか

何をもって「最強」と定義するのか次第ですが、主メモリ、プログラムカウンタ、インストラクションレジスタ、算術論理演算ユニット、アキュムレータの他にワークレジスタを一個だけ使うアーキテクチャで、OSやコンパイラを走らせることのできるCPUは理論的に考えて、図6〜図9のいずれかの構成になると思います。

私感ではありますが、相対ジャンプを実装しないのなら図7が、相対ジャンプを実装するならば図9が、最も作りやすいアーキテクチャだと思います。

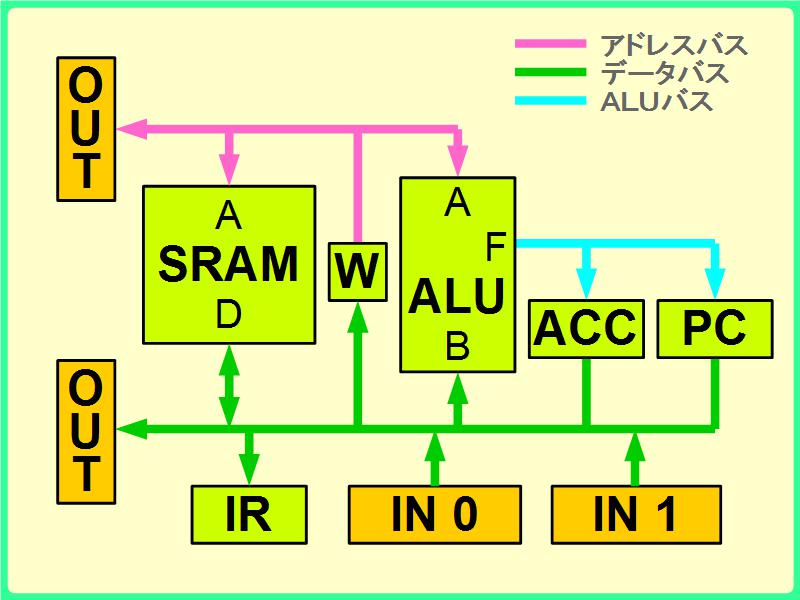

図10は最終的に決定した最も単純かつ実用に耐えうるTTLコンピュータの構成図です。

図9を整形して入出力を加えたものです。

図には出力ポート(OUT)が2つありますが、これはLEDに直結します。このLEDは手動でプログラミングをする際の、アドレス値表示器とデータ値表示器を兼ねます。

また入力ポートも2つありますが、こちらは2つである必然性はなく、最低1つあれば幾つでも構いません。

本当の設計はここからです

アーキテクチャの決定は設計の「土台」にすぎません

コンピュータがプログラムを実行する様子を、都市における人間の生産活動に例えるなら、本ページで述べたアーキテクチャは、単に建物を建て道路を作っただけの「無人都市」の状態に過ぎません。

この後は、命令セットを決めて、実際にCPU内でその命令を実現するためのシーケンス(CPU内部の動作順序)を決めて、さらにそのシーケンス通りに各部品を動かすための制御回路を決めていく事になります。

おそらく、ここで決めた「アーキテクチャ設計」は、手作りコンピュータ全体の設計の内、ソフトの設計を除くハードの設計に限っても、全体の5%にも満たないと思います。

(2015年5月30日)草稿のまま公開