RETROF-16Kの回路設計(1)

基本クロック生成回路の設計

動作周波数の決定

CPUの処理速度はCPUに与えるクロックの周波数に比例します。この周波数は「速ければ速いほど良い」のは当然ですが、半導体部品には必ず最大動作周波数があり、その値を超すと正常動作は保証されません。本機で用いている標準ロジック(74LSシリーズ)の最大動作周波数は数10MHzほどです。但しこれは理想的な環境(電源、配線容量、負荷など)で動作させた場合です。また論理ゲートを多段接続するとその段数分の遅延が発生しますので、個々の部品は数10MHzで動作可能でも、回路全体では1MHz以下でも正しく動作しないこともあります。

本機は、過去に作成し動作に成功したRETROFシリーズの最大クロックが4MHzであったこともあり、それを超す速度での動作を目標としました。

最終的に決定したクロックは6.75MHzです。この値は、本機の画像表示回路のピクセルクロック(ある画素の表示色を与えてから、次の画素の表示色を与えるまでの時間)である27.000MHzの1/4の値になります。

ピクセルクロック発振器とCPUの動作用のクロック発振器を個別に用意するのは無駄ですので、ピクセルクロックを分周して簡単に作れる値である6.75MHzをCPUの動作クロックとして使う事にした結果、こうなりました。

画像は本機のピクセルクロック作成に用いた水晶発振子内蔵の27.000MHzのPLL発振器。

5Vを与えるだけでTTLに直結できる矩形波を得ることができる汎用部品(300円ほどで入手可能)。CPUクロックはこれを4分周した6.75MHzを用いる。27.000MHzという値は使用する液晶モニタの規格値から算出した値。算出方法の詳細は「グラフィック表示回路の設計」編で紹介予定。

手動クロック回路

CPUに与えるクロックは速いほど良いのですが、手作りコンピュータは回路のデバッグの為に目で追える速度で動かす仕組も必須です。

前作RETROF-16Hでは、基板上にコネクタのみを用意し、手動クロック装置を必要に応じて接続する方法を取りましたが、付けたり外したりするのが結構面倒だったので今回はオンボードとしました。

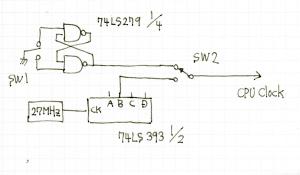

手動クロックは、マイクロスイッチ(図のSW1)をRSフリップフロップ(74LS279)に接続しチャタリングを確実に除去しています。

手動クロックは、マイクロスイッチ(図のSW1)をRSフリップフロップ(74LS279)に接続しチャタリングを確実に除去しています。

自動クロックは27MHzのPLL発振器をカウンタ(74LS393)で4分周し、6.75MHzを作成します。74LS393の規格上の最大動作周波数は25MHzですので推奨できる設計ではありませんが、特に問題なく動いています。

両者の切り替えはトグルスイッチ(図のSW2)で行います。

ステージカウンタとステージデコーダ

CPUクロック自体は単なる矩形波ですので、それ自体は何の情報も持ちません。まずはこれをN分周し、より細かなタイミング信号を生成する必要があります。Nの値は1つの命令を実行するのに必要なクロック数とするのが一般的です。本機は全ての命令を11クロックで処理しますので、Nの値は11固定です。

更に本機は2クロックを1組として「ステージ」を構成します。「ステージ」は「命令を実行する段階」という意味ですが、厳密な意味は人によって異なります。本書で用いるステージの意味を下記に図示します。

・ステージを表す文字としてΦ(ファイ)を使用します

・Φ1~Φ6までの6つのステージで1つの命令が実行されます

・1つのステージは2クロック(Φ6のみ1クロック)です

・ΦCKはΦ1~Φ5の各ステージの中央で立ち上がる信号です

| 状態 | 停止中 | 最初の命令を実行中 | 次の命令を実行中 | |||||||||||||||||||||||||||||||||||||||||||||||||

| ステージ | Φ1 | Φ2 | Φ3 | Φ4 | Φ5 | Φ6 | Φ1 | Φ2 | Φ3 | Φ4 | Φ5 | Φ6 | Φ1 | |||||||||||||||||||||||||||||||||||||||

| ΦCK | ||||||||||||||||||||||||||||||||||||||||||||||||||||

| CPUクロック | ||||||||||||||||||||||||||||||||||||||||||||||||||||

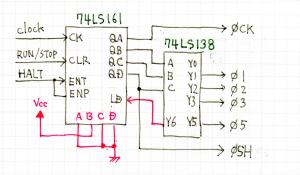

以下が上記の各タイミング信号を実際に発生させる回路です。バイナリカウンタ74LS161と、3bitデコーダ74LS138を使用しました。

clockには前述した6.75MHzのCPUクロックを与えます。

clockには前述した6.75MHzのCPUクロックを与えます。

RUN/STOPは停止ならLを実行ならHを与えます。この信号がLの間はカウンタの値は0のままとなり、各種タイミング信号はアクティブになりません。

HALTにはHALT命令を検知した時にLを与えます。カウンタのENP/ENT(カウントの許可を行う端子)に接続されているので、この信号がLになるとカウントが止まり、CPUも動きが「凍結」します。この解除は手動でSTOPボタンを押すことによってのみ解除可能です。停止位置(停止番地)からの再実行機能はありません。

16進カウンタである74LS161を11進カウンタとして用いる為に、カウント値が12になった状態(デコーダー74LS138のY5がLになった状態)でクロックパルスが入ると値2をロードするように細工しています(回路図中の赤色で書かれた配線)。

これにより74LS161は2~12を繰り返す11進カウンタとして機能します。(0~10を繰り返すのではない点に留意)

この回路が生成するのは、各ステージの期間に応じてLとなるΦ1~Φ6のステージ信号(※1)と、各ステージの中央で立ち上がる信号、ΦCKです。

また、Φ4~Φ6ステージの間は連続してLとなるΦSH(SHはSeconf half=後半)信号も生成します。

このΦSH信号は、1つの命令を処理する際に「命令の種類に拘らず共通の処理(命令フェッチ等)を行う前半3ステージ」と「命令毎に処理が異なる後半3ステージ」を識別する為に用います。(※2)

※1 Φ4信号とΦ6信号は使用しないので回路図には記載していません。

※2 初期設計では「前半が8クロック4ステージ、後半も8クロック4ステージ」というシンプルなタイミング構成でした。その後、処理速度を上げる工夫を繰り返した結果、「前半が6クロック3ステージ、後半も6クロック3ステージ」となり、更に最後の1クロックを省略し、「前半が6クロック3ステージ、後半が5クロック3ステージ」という中途半端な数字となりました。この辺りはまだまだ改良の余地がありそうです。

命令レジスタに見るステージ信号の供給例

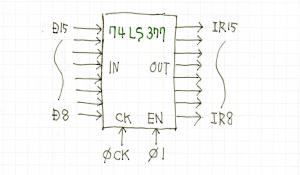

ステージ信号の利用例として、命令レジスタ(IR=Instruction register)の制御回路を紹介します。この回路が行う動作は一般に「命令フェッチ」と呼ばれ、命令フェッチを行う期間は「命令フェッチサイクル」と呼ばれます。本機では第1ステージが命令フェッチサイクルに相当します。

本機の命令レジスタを構成するTTLは8bitのD-FFである74LS377が1個のみです。

本機の命令レジスタを構成するTTLは8bitのD-FFである74LS377が1個のみです。

74LSシリーズには8bitのD-FFは何種類かありますが、クロックイネーブル端子(Hにするとクロックが無視される端子)があるのはこの74LS377のみです(※)。

このクロックイネーブル端子が存在する事により、ここにΦ1を与え、クロック端子にΦCKを与えるだけで、命令レジスタの制御が完成します。

74LS377の入力はデータバスの上位8bit(命令のオペコード部分)です。

この値を次の命令を受け取るまで保持するのが、命令レジスタである74LS377の役目となります。

※厳密に言うと742520等、74シリーズの中でも特注品に近い型番には8bitのイネーブル端子付D-FFは存在します。(一般には入手が困難)

本項(基本クロック回路周辺)のまとめ

ここまでがコンピュータの制御回路の基礎部分に当たります。コンピュータの制御回路はコンピュータにおける司令塔ですから、言い換えると、ここまでの回路がコンピュータの「最重要回路」に相当します。

よく加算や減算等を行う「演算回路」がコンピュータの最重要回路だと誤解している方がおりますが、コンピュータの演算回路はANDゲートやORゲートと同様、入力が決まれば出力が決まる単純な組合せ回路に過ぎません。「電卓」を設計するならば、演算回路は最も重要な回路の一つですが、「コンピュータ」を設計するならば、制御回路が最も重要な回路となります。

余談ですが、大学(あるいは高専、大学院)の卒業研究等にて、「コンピュータの作成」と称して「演算回路」のみを作成した事例を目にする事があります。これは明らかに間違いであり、指導担当教員が訂正させるべき事だと思います。

機械語命令別の制御信号の生成

次回はここからです。(いつ書くかはわかりません)\^o^/