RETROF-16Mの主な内部素子と制御信号

本ページの概略

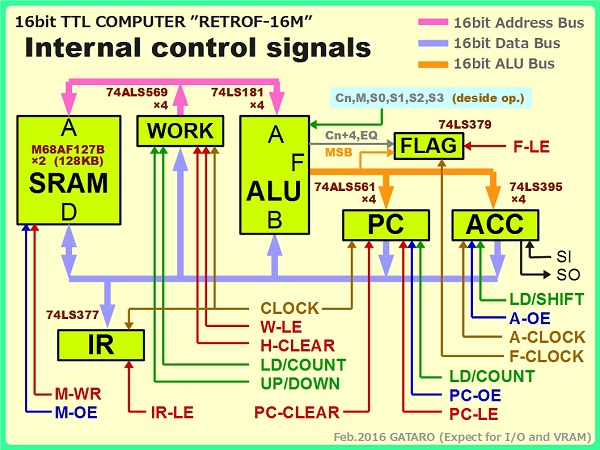

図1はRETROF-16MのCPU部分を構成する内部素子とその制御信号の概略図です。

本頁の前半はこの図1に対する説明、後半は図1以外の部品(入出力関係と補助的な回路の部品)の説明となります。

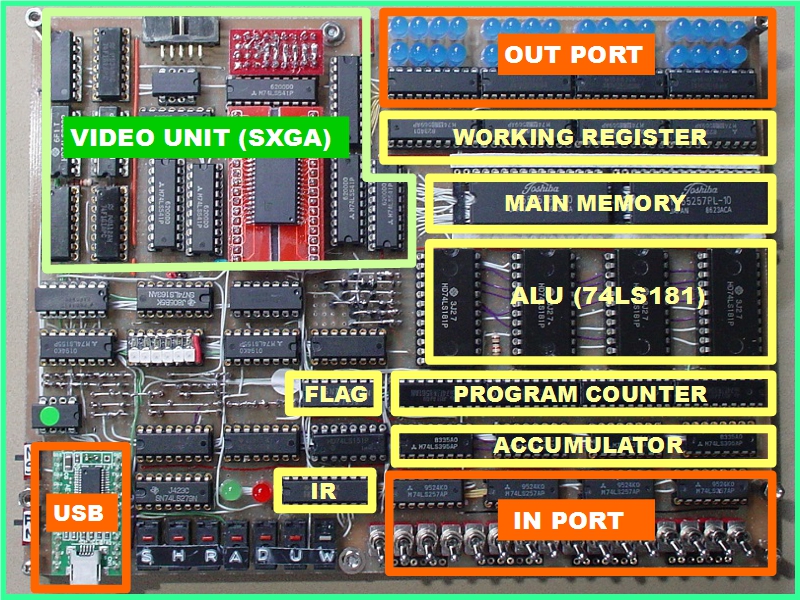

図2は完成したRETROF-16Mの基板(200mm×150mm)です。

この図の木枠で囲んだ部分が図1に示した「CPU部分を構成する内部素子」にあたります。

PC(Program Counter、74ALS561×4)

4bitのカウンタを4個使い、16bitのバイナリカウンタを構成します。

LSファミリーではなくALSファミリーを使用したのは、LSの入手が困難であったためで、電気的特性の差異を考慮したものではありません。

| 信号名 (回路図上での信号名) | ピン番号 | この信号が持つ意味と働き |

|---|---|---|

| CLOCK (WPΦ) | 2 | 立ち上がりで動作、WORK、IR、FLAGのクロックと共通 |

| PC-LE (PLD) | 11 | Lの時にクロック立上がりに同期してデータを読込む |

| PC-OE (POE) | 17 | Lで出力有効、Hで出力はHi-Z |

| LD/COUNT(PCE) | 7,12* | Lの時にクロック立上がりに同期してカウントアップ |

| PC-CLEAR(DMA) | 8 | Lでクリア(非同期)、実行時は常にH、停止時は常にL |

(*) 4つの74ALS561の最下位の7,12番ピン、他は前段のRCOに接続。詳細は回路図参照方

SRAM (Main Memory、M68AF127B(55ns)×2)

アドレス線17本、データ線8本のSRAM*です。これを2個使いデータ幅16bitの主メモリを構成します。アドレス線の最上位(A16)は常にGNDに接続とし、アドレス空間も16bitのSRAMとして使用します。

| 信号名 (回路図上での信号名) | ピン番号 | この信号が持つ意味と働き |

|---|---|---|

| M-WR (MWR) | 29 | Lで書き込み |

| M-OE (MOE) | 22 | Lで出力有効、Hで出力はHi-Z |

(*) TTLではありません。RETROF-16MはメモリとUSB通信関係はTTL以外のICも使用しています

IR(Instruction Register 74LS377)

8bitのD-FFです。機械語命令の上位8bitを格納します。

| 信号名 (回路図上での信号名) | ピン番号 | この信号が持つ意味と働き |

|---|---|---|

| CLOCK (WPΦ) | 11 | 立ち上がりで動作、WORK、PC、FLAGのクロックと共通 |

| IR-LE (名称無) | 1 | Lの時にクロック立上がりに同期してデータを読込む |

WORK(Working Register or Multipurpose Register、74ALS569 ×4)

4ビットのアップダウンカウンタを4つ並べた16ビットのカウンタです。

カウント機能は、プログラム停止時に手動でプログラムを書き変える際にのみ使用します。

実行時はカウント機能は利用せず、「主メモリに与えるアドレスの保持」と「ALUに与える非演算子の保持」を兼ねる単なるD-FFとして動作します。

LSではなくALSを使用している理由はプログラムカウンタと同じです。

| 信号名 (回路図上での信号名) | ピン番号 | この信号が持つ意味と働き |

|---|---|---|

| CLOCK (WPΦ) | 2 | 立ち上がりで動作、IR、PCのクロックと共通 |

| WLE (WLE) | 11 | Lの時にクロック立ち上がりでデータを読み込む |

| H-CLEAR (WHC) | 9* | Lで上位8ビットがクリア(クロック同期)される |

| LD/COUNT(DMA) | 7,12** | Lでカウント(同期)。実行時は常にH、停止時は常にL |

| UP/DOWN (WUD) | 1 | Hでcount up、Lでdown。実行時は意味を持たない |

(*) 4つの74ALS569の上位2つの9番ピン、下位2つの9番ピンは常にH。詳細は回路図参照方

(**) 4つの74ALS569の最下位の7,12番ピン、他は前段のRCOに接続。詳細は回路図参照方

ALU (Arithmetic Logic Units、74LS181 ×4)

4bitの値と4bitの値の演算を行う74LS181を4個使い16bitの演算器を構成します。

| 信号名 (回路図上での信号名) | ピン番号 | この信号が持つ意味と働き |

|---|---|---|

| Cn(Cn) | 7* | キャリー入力、加算と減算で論理が逆である点に注意 |

| M(M) | 8 | Hで論理演算、Lで算術演算指定となる。 |

| S3〜S0(S3〜S0) | 3〜6 | 演算種別の指定、詳細は74LS181の資料を参照方 |

| A=B(EQ) | 14 | 演算結果が0xFFFFの時にHとなる。 |

| Cn+4(Cn4) | 16** | キャリー出力、加算と減算で論理が逆である点に注意 |

(*) 4つの74LS181の最下位の7番ピン、他は前段のCn+4に接続。詳細は回路図参照方

(**) 4つの74LS181の最上位の16番ピン、他は後段のCnに接続。詳細は回路図参照方

ACC(Accumulator、74LS395×4)

4bitの単方向シフトレジスタ74LS395を4個使い16bitの単方向シフトレジスタを構成します。シフトは右シフト(値を半分にするシフト)のみ可能です。双方向シフトレジスタを用いなかった理由は、3S出力が可能かつパラレルの入力線が独立している双方向シフトレジスタが74シリーズには存在しないためです。

| 信号名 (回路図上での信号名) | ピン番号 | この信号が持つ意味と働き |

|---|---|---|

| A-CLOCK(ACK) | 10 | クロック、74LS395は立下り動作である事に注意 |

| A-OE(AOE) | 9 | Lで出力有効、Hで出力はHi-Z |

| LD/SHIFT(ALS) | 7 | Hでロード、Lでシフト。(クロック同期) |

| SI(SI)* | 2 | シフト入力、USB接続によるデータ転送時以外は常に0 |

| SO(SO)* | 11 | シフト出力、USB接続によるデータ転送時にのみ使用 |

(*) RETROF-16MはUSBケーブルで接続することにより、WindowsPCと主メモリ内容のデータ交換が可能です。SIとSIはこのデータ交換時にのみ使用する

FLAG (Flag Reguster、74LS379)

4bitのD-FFです。演算命令実行時に変化する3種類のフラグを保持します。フラグは3種類ですので4bitのうち、1ビットは使用しません。

| 信号名 (回路図上での信号名) | ピン番号 | この信号が持つ意味と働き |

|---|---|---|

| F-CK(WPΦ) | 9 | 立ち上がりで動作、WORK、IR、PCのクロックと共通 |

| F-LE(G) | 1 | Lの時にクロック立ち上がりでデータを読み込む |

| Cn+4(CARRY) | 5 | キャリーフラグ入力、ALUのCn+4に接続 |

| EQ(EQUAL) | 13 | フルフラグ*入力、ALUのA=Bに接続 |

| MSB(F15) | 4 | サインフラグ**入力、演算結果の最上位ビットに接続 |

| 使用せず | 12 | 使用しない1bitの入力(非使用を明示するために掲載) |

(*) ALUの2入力の値が等しい時ではなく、演算結果が0xFFFFの時にHとなるのでこの名称を用いる

(**) RETROF-16Mが扱う値にサイン(正負符号)はないが、便宜上サインフラグと称している

その他の使用素子

概略

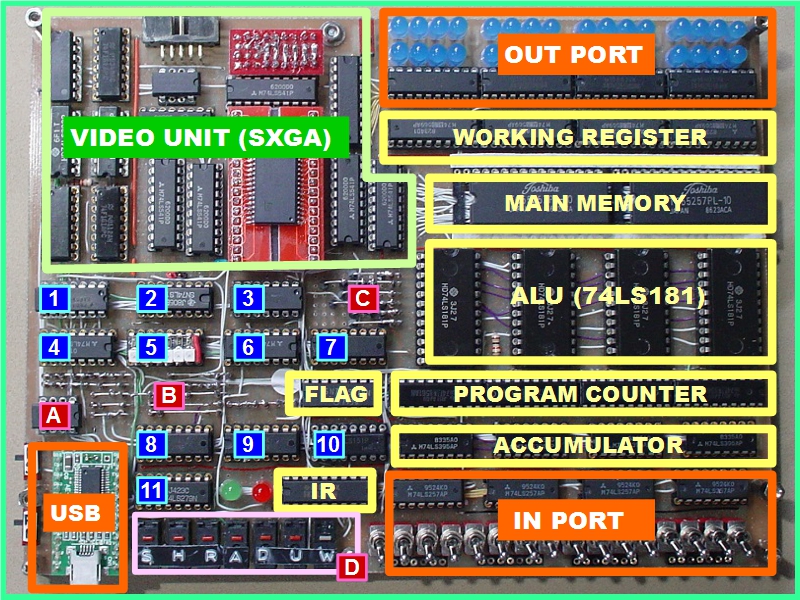

ここから先が本頁の「後半」になります。基板上に実装した部品のうち、前半では解説しなかった部品の説明になります。図3の黄色の枠で示した部分以外が対象となります。

VIDEO UNIT

一般のパソコン用のSXGA(1280×1024画素)液晶ディスプレイに対する画像信号を生成します。クロックジェネレータとSRAM(ビデオメモリ)以外は全てTTLで構成されています。

この回路の詳細は「VIDEO UNIT編」として別ページで別途詳細を解説予定*です。

(*)2016年3月現在。完成次第リンクを張る予定。(2016年3月記)

OUT PORT(74ALS563×4)

8bitのラッチ74ALS563を4個並べ、32bitの出力ポートを構成しています。その入力線はアドレスバスとデータバスに直結、出力線は基板上の32個の青色LEDに直結しています。

LSではなくALSを使用している理由はプログラムカウンタと同じです。

| 回路図の信号名 | ピン番号 | この信号が持つ意味と働き |

|---|---|---|

| OUT | 11 | Lで出力ホールド、Hで入出力貫通 |

IN PORT(74LS273×4)

2系統の入力を選択可能な4bitの3Sバッファ74LS273を4個並べ、16ビット2系統の入力ポートを構成しています。その出力線をデータバスに直結しています。入力線の一系統は基板上の16個のトグルスイッチに、もう一系統は外部に接続するために基板上に配置したコネクタに接続しています。

| 回路図の信号名 | ピン番号 | この信号が持つ意味と働き |

|---|---|---|

| IOE | 15 | Lで出力有効、Hで出力はHi-Z |

| IAB | 1 | Lで入力系統Aを選択、Hで入力系統Bを選択 |

USB(USB Interface、FT245RL)

Windowsパソコンから本機の主メモリを変更するためのUSBポートです。USBポートをTTLで構築するのは困難であったため、この回路だけはTTLでの構築をあきらめ、FTDI社のUSB-パラレル変換チップ、FT245RLを使用しています。

その他のTTL(図3の1〜11、※欄は回路図の部品番号)

| 番号 | TTL型番 | ※ | このTTLの概略と働き |

|---|---|---|---|

| 1 | 74LS08 | U35 | 2入力ANDゲート×4回路、 雑多な論理信号作成用 |

| 2 | 74LS163 | U27 | 16進同期カウンタ、インストラクションカウンタとして使用 |

| 3 | 74LS00 | U41 | 2入力NANDゲート×4回路、雑多な論理信号作成用 |

| 4 | 74LS155 | U29 | 2bit→4のデコーダ×2回路、機械語の命令デコード用 |

| 5 | 74LS138 | U28 | 3bit→8のデコーダ、インストラクションデコーダ、上記2をデコード |

| 6 | 74LS155 | U30 | 2bit→4のデコーダ×2回路、機械語命令のデコード用 |

| 7 | 74LS138 | U25 | 3bit→8のデコーダ、命令コード→ALUに与える演算コードの変換用 |

| 8 | 74LS138 | U36 | 3bit→8のデコーダ、機械語命令のデコード用 |

| 9 | 74LS138 | U31 | 3bit→8のデコーダ、機械語命令のデコード用 |

| 10 | 74LS151 | U42 | 8→1のセレクタ、フラグレジスタの出力を選択するために使用 |

| 11 | 74LS279 | U39 | 4回路のRS-FF、3回路をチャタリング防止に、1回路は単にNOTとして使用 |

| (*) | 74LS541 | U40 | 8ビットの3Sバッファ、USBインタフェイスのバッファ |

(*)図3ではUSBユニットの下に位置しています。直接見えないため番号を振っておりません

その他の部品(TTL以外)

| 記号 | 部品型番 | この部品の概略と働き |

|---|---|---|

| A | SG-8002DC(5V用) | 10.000MHzのクロック発生器です。上記の番号2のクロックとなる |

| B | SD103A(計42本) | 各デコーダの出力から、各素子の制御信号を作るダイオードマトリクス |

| C | 1S3(計16本) | ALUに与える演算コードを作るダイオードマトリクス |

| D | D2F相当品(7個) | 手動で主メモリ内容変更/実行/停止をするためのマイクロスイッチ群 |

全ての部品リストではありません。上記以外にもダイオード、LED、抵抗、コンデンサ等を使用しています

(Mar. 2016)