RETROF-16Mの命令デコード回路と実行タイミング

下記資料はクリックすると別ウィンドウで開きます。

・RETROF-16Mの内部素子 (←開けます)

・RETROF-16Mの回路図とその解説 (←現在工事中、開けません)

・RETROF-16Mの命令セット (←開けます)

尚、本頁も含めこれらの頁は現在も校正中です。(仮公開の状態)

後日、構成や内容が大きく変わる可能性が高い事を御了承願います。

ステージとステージ信号

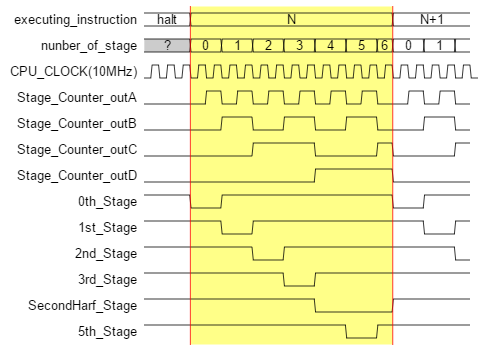

RETROF-16Mは1つの命令を13クロック(1クロックは10MHz)で処理します。

説明の便宜上この13クロックを7つの区間に分け、各区間を「ステージ」と呼びます。

各ステージの長さは2クロック分(但し第6ステージだけは1クロック分)です。

現在実行中のステージを示す信号は16進カウンタ74LS163とデコーダ74LS138で作成され、その信号を含む主な信号を図示したのが下記となります。

第4、第6ステージの実行中を表す信号は上図では省略しています。代りに第4〜第6ステージのいずれかを実行中であることを示す信号(図ではSecondHarf_Stage、以下StageSと略記)を図に加えています。

個々の素子を制御する信号(素子制御信号)

ステージ信号とIR(命令レジスタ)が出力する信号を組み合わせると、任意の命令の任意のステージに対応する信号を作ることができます。この信号がコンピュータを構成する個々の素子を制御する信号(素子制御信号)となります。

例えば、プログラムカウンタをインクリメントしたりアキュムレータの値を更新する信号がこれにあたります。

256種類の命令を7つのステージで処理する場合、単純計算では256×7で1792種類の素子制御信号を作り出すことができます。しかし、例えば「加算命令」と「減算命令」は演算種別が異なるだけで、各ステージで必要とする信号は全く同じですし、「無条件分岐命令」と「条件分岐命令」も分岐条件が異なるだけで、各ステージで必要とする信号は全く同じです。従って実際に必要となる素子制御信号の数は1792よりもはるかに少ない数になります。

RETROF-16Mの場合、ステージ信号とIR(命令レジスタ)が出力する信号を組み合わせにより作られる素子制御信号わずか30種類です。以下がその30種類の信号線を作成する回路の略図(回路図の命令をデコードをする部分回路のみを抽出し簡略化した図)です。

左端の青字の「STAGE n」は処理中のステージ番号を示す信号で、左端赤字の「IR bit n」はIRの出力です。矩形は個々のデコード素子(TTL)で、右肩のUnは回路図の部品番号に対応します。「G」はGATEの略でこの信号をアクティブにならないと、デコード素子の出力はいずれもアクティブにはなりません。

上図の右側に並ぶデコード出力線が素子を制御する30種の信号線です。

例えば1番上の「XXXXXXXX-S0 Fetch PC」は、命令の種別に関わらずステージ0で必要となるプログラムカウンタの値を取り出す為の信号です。

同じく「11X111XX-S5 HALT」は、命令コードが11X111XXのときの第5ステージの時にアクティブになるHALT信号を意味します。

これらのデコード出力線が、信号衝突防止用のダイオードを介してRETROF-16Mを構成する各素子(プログラムカウンタ、アキュムレータ、ワーキングレジスタなど)の制御を行います。上図のどのデコード信号で、どの素子がどのように制御されるかの詳細は次項の表を参照願います。

各ステージで生成される素子制御信号とその働き

ステージ0・1

ステージ0と1は全命令で共通動作です。機械語命令の上位8bitをIR(命令レジスタ)に、下位8bitをワーキングレジスタに格納するのが目的です。

ワーキングレジスタの書き換えは各ステージの中間で行われるため、ステージの開始時点と終了時点でワーキングレジスタの値は異なります。

| 命令種別 |

ステージ | Wレジスタ の内容 |

データバス の内容 |

内部で生じる転送 |

|---|---|---|---|---|

| 全命令共通 |

0(開始) |

不定 | PC | PCの値→W |

| 0(終了) | PCの値 | |||

| 1(開始) | PCの値 | Wが示す メモリ値 |

M(W)の上位8bit→IR 下位8bit→W 0→Wの上位8bit PC+1→PC |

|

| 1(終了) | 8bit即値 |

ステージ2・3

ステージ2と3の動作は命令のアドレッシングモード(修飾種別)により異なります。

いずれもステージ3が終了した時点でワークレジスタに下記表の黄色で示す値を格納するのが目的です。

| 修飾種別 (命令コード) |

ステージ | Wレジスタ の内容 |

データバス の内容 |

内部で生じる転送 |

|---|---|---|---|---|

| 8bitリテラル (XXXXXX00) |

2(開始) |

8bit即値 | 不定(Hi-Z) | 何もしない (Wレジスタは8bit即値が格納されたまま) |

| 2(終了) | ||||

| 3(開始) | ||||

| 3(終了) | ||||

| レジスタ直接 (XXXXXX01) |

2(開始) |

8bit即値 | 不定(Hi-Z) | 何もしない |

| 2(終了) | ||||

| 3(開始) | 8bit即値 | Wが示す メモリ値 |

Wが示すメモリの内容(仮想レジスタ値)→W | |

| 3(終了) | レジスタ値 | |||

| レジスタ間接 (XXXXXX10) |

2(開始) |

8bit即値 | Wが示す メモリ値 |

Wが示すメモリの内容(仮想レジスタ値)→W |

| 2(終了) | レジスタ値 | |||

| 3(開始) | レジスタ値 | 仮想レジスタが示すメモリの値→W | ||

| 3(終了) | メモリ値 | |||

| longリテラル (XXXXXX11) |

2(開始) |

8bit即値 | PC | PCの値→W |

| 2(終了) | PC | |||

| 3(開始) | PC | PCが示す メモリ値 |

Wが示すメモリの内容(命令2ワード目)→W PC+1→PC |

|

| 3(終了) | 2ワード目 |

後半ステージ(ステージ4〜6)

後半ステージは分岐命令、演算命令、その他の命令に大別され、それぞれ動きが異なります。後半ステージの期間中のアドレスバスはステージ2・3で決定した値を維持しており、その値は変化しません。

| 命令種別 |

命令コード | データバス の占有者 |

内部の動作が生じる タイミング |

内部で生じる動作 (●は命令コード中のPで決まる演算記号) |

|---|---|---|---|---|

| 分岐命令 |

0XXXPPXX |

PC | ステージ5の中央 | (分岐条件が一致したら)PC●W→PC |

| 演算命令 | 10XPPPXX | Acc | ステージ5の終り | Acc●W→Acc (CMPはAccに代入しない) |

| SFT命令 | 11X000XX | 無し(Hi-Z) | ステージ5の終り | Accを右シフト、MSBには0を代入 |

| PLD命令 | 11X001XX | PC | ステージ5の終り | PC→Acc |

| IN命令 | 11X010XX | 入力ポート | ステージ5の終り | 入力ポート→Acc |

| LDV命令 | 11X011XX | 画像メモリ | ステージ5の終り | VRAM(W)→Acc |

| STV命令 | 11X100XX | Acc | ステージ5の全区間 | Acc→VRAM(W) |

| OUT命令 | 11X101XX | Acc | ステージ5の全区間 | W→出力ポートA、Acc→出力ポートB |

| ST命令 | 11X110XX | Acc | ステージ5の全区間 | Acc→Wで示される主メモリ |

| HALT命令 | 11X111XX | 無し(Hi-Z) | ステージ5の始まり | ステージカウンタの強制停止 |